“不积跬步,无以至千里;不积小流,无以成江海。”

-- 荀子《劝学篇》

"No accumulation of steps, can't lead to thousand miles.

No integration of streams, can't result in rivers and oceans."

About Me

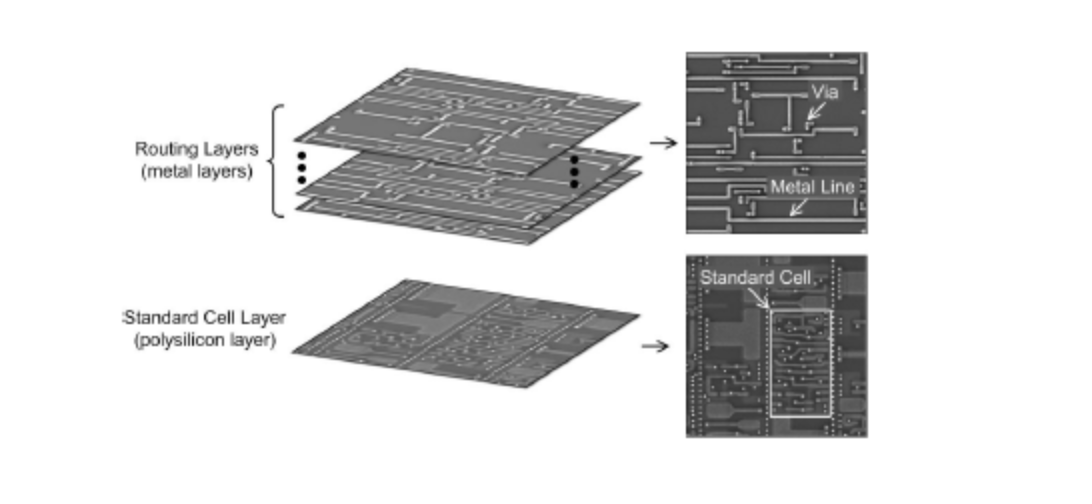

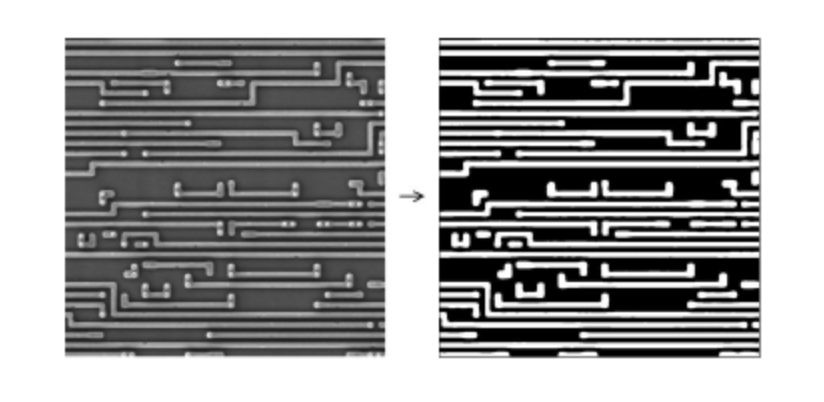

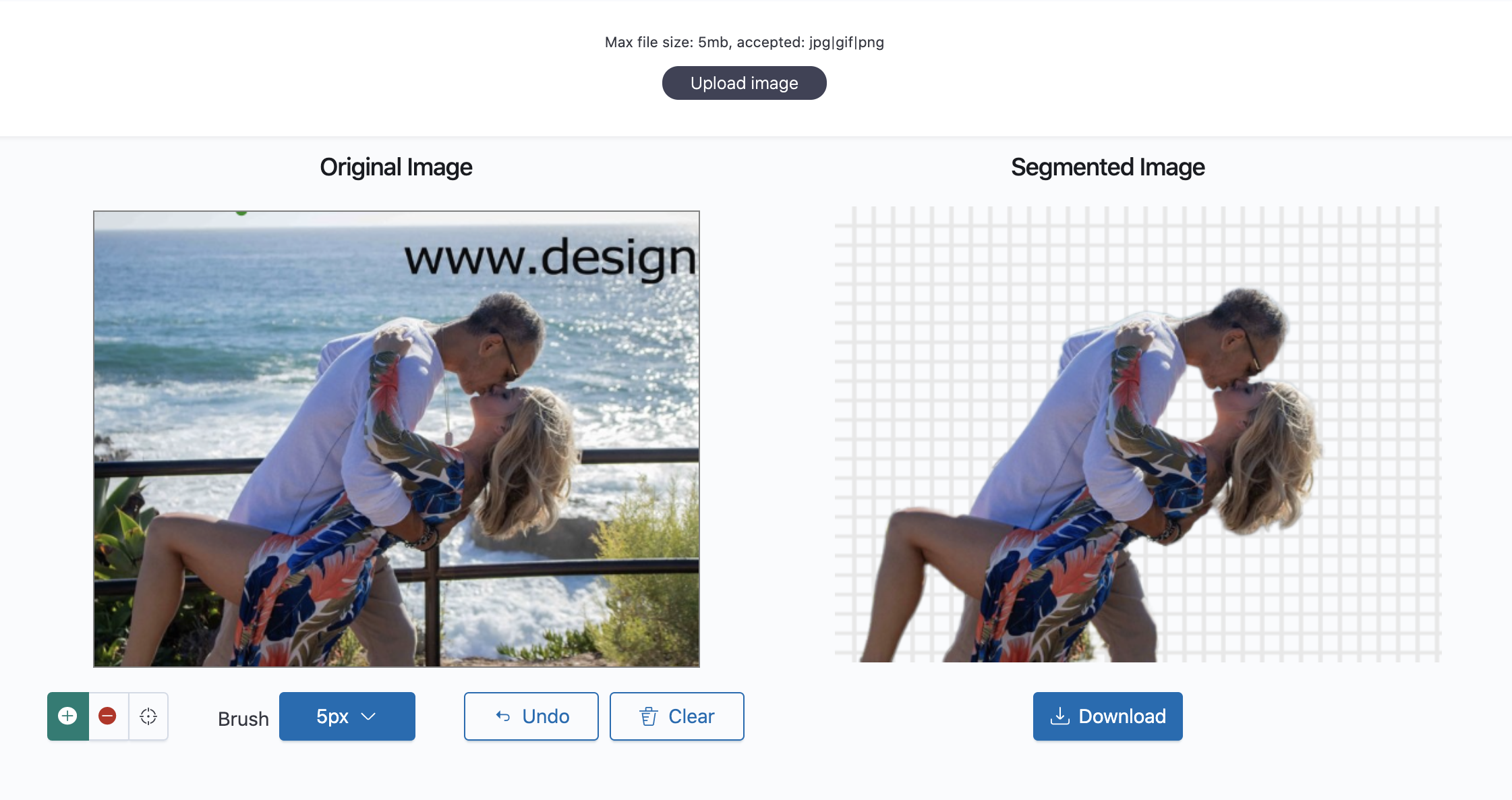

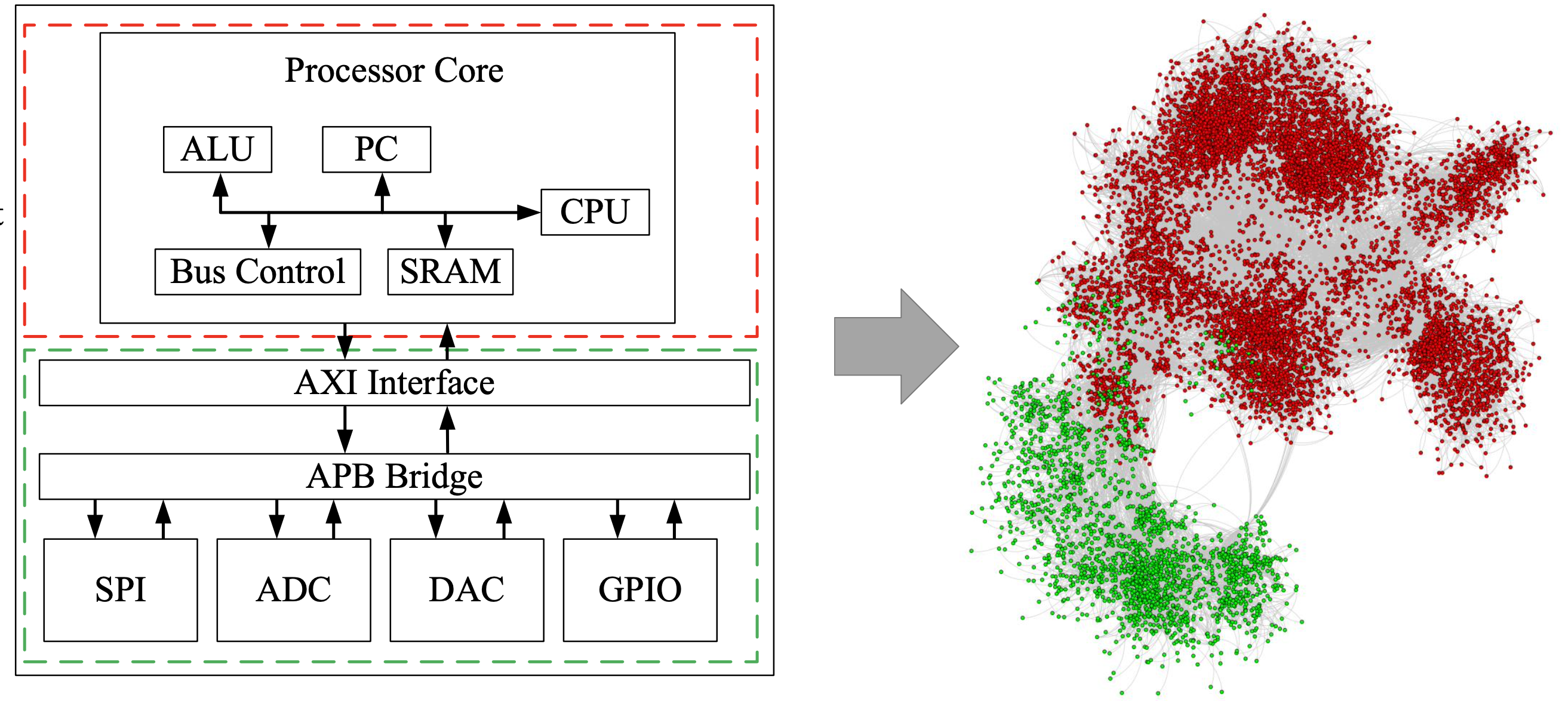

I am a Ph.D. graduate from Nanyang Technological University (NTU), Singapore. My research interests span the areas of circuit netlist analysis, Deep Learning (DL) and Graph Learning (GL). The objective of my research is to perform robust reverse engineering of circuit netlist of Integrated Circuits (ICs) through graph analysis and graph learning.I received my bachelor's degree in Electrical and Electronics Engineering from NTU in 2018. I have worked in Micron Semiconductor Asia for 1 year before I started my Ph.D in 2020. I am very fortunate to be fully sponsored by EDB-Industrial Postgraduate Program (IPP) under Shopee. I spent 50% of my time working on industrial projects in collaboration with experts in Shopee, and the other 50% of my time working on my Ph.D research. As such, I am exposed to both industrial experience in application development, staging and servicing and academic experience in conducting research works.

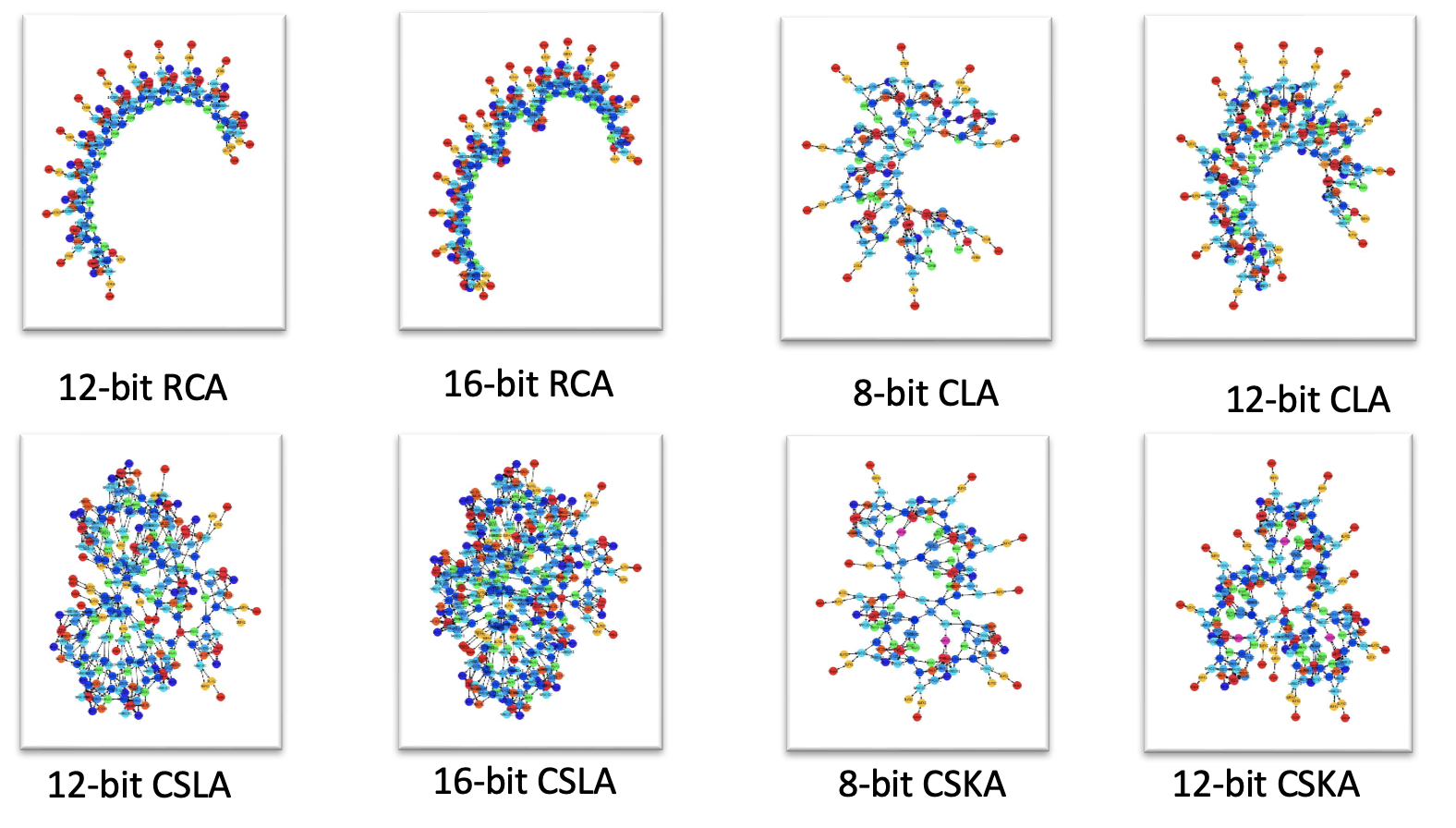

My project experiences cover both Computer Vision (CV) and Graph Machine Learnin (GML). This includes Deep Learning models for image segmentation on IC images and online shopping images, Deep Learning models for text detection on online advertisement, graph machine learning models for graph partitioning and graph classification on circuit netlist as graphs, attributed knowledge graph clustering for product categorization, and more. Some of my past projects (and publications) are shown in the coresponding section below.

Recent Works & Publications

See details →

GraphClusNet: A hierarchical graph neural network for recovered circuit netlist partitioning

Netlist Analysis | Graph Partitioning | Graph Neural Network

See details →

GraphClusNet: A hierarchical graph neural network for recovered circuit netlist partitioning

Netlist Analysis | Graph Partitioning | Graph Neural Network

See details →

Asic circuit netlist recognition us- ing graph neural network

Netlist Recognition | Graph Neural Network

See details →

Asic circuit netlist recognition us- ing graph neural network

Netlist Recognition | Graph Neural Network

[1] Xuenong Hong, Tong Lin, Yiqiong Shi, and Bah-Hwee Gwee, "Deep learning for automatic ic

image analysis," In IEEE 23rd International Conference on Digital Signal Processing (DSP), pages

1–5, 2018.

[2] Tong Lin, Yiqiong Shi, Na Shu, Xuenong Hong, and Bah-Hwee Gwee, "Deep learning-based

image analysis framework for hardware assurance of digital integrated circuits," Microelectronics

Reliability, 123(6):114196, 2021.

[3] Xuenong Hong, Tong Lin, Yiqiong Shi, and Bah-Hwee Gwee, "Asic circuit netlist recognition using

graph neural network," In IEEE International Symposium on the Physical and Failure Analysis

of Integrated Circuits (IPFA), pages 1–5, 2021.

[4] Xuenong Hong, Tong Lin, Yiqiong Shi, and Bah-Hwee Gwee, "Graphclusnet: A hierarchical

graph neural network for recovered circuit netlist partitioning," IEEE Transactions on Artificial

Intelligence, 1(1):1–15, 2022.

[5] Yee Yang Tee, Xuenong Hong, Deruo Cheng, Chye Soon Chee, Yiqiong Shi, Tong Lin, Bah Hwee Gwee, "Patch-based Adversarial Training for Error-aware Circuit Annotation of Delayered IC Images," in IEEE Transactions on Circuits and Systems II: Express Briefs, 2022.

[6] Yee Yang Tee, Xuenong Hong, Deruo Cheng, Tong Lin, Yiqiong Shi, Bah Hwee Gwee, "Unsupervised graph-based image clustering for pretext distribution learning in IC assurance", in Microelectronics Reliability, 2023.

[7] Xuenong Hong, Yee Yang Tee, Tong Lin, Yiqiong Shi, Deruo Cheng, Er Huang, Bah Hwee Gwee, "GoCLIP: Graph one-class CLassification for Intellectual Property Circuit Identification”, IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), 2023.

[8] Erdong Huang, Xuenong Hong, Tong Lin, Yiqiong Shi, Bah Hwee Gwee, "GRACER: Graph-based Standard Cell Recognition in IC Images for Hardware Assurance", 49th Annual Conference of the IEEE Industrial Electronics Society (IES), 2023.

[9] Xuenong Hong, Zilong Hu, Han Zhang, Yee-Yang Tee, Tong Lin, Yiqiong Shi, Deruo Cheng, Bah-Hwee Gwee, "MLConnect: A Machine Learning Based Connection Prediction Framework for Error Correction in Recovered Circuit", IEEE International Symposium on Circuits and Systems (ISCAS), 2024

[10] Xuenong Hong, Yee Yang Tee, Zilong Hu, Tong Lin, Yiqiong Shi, Deruo Cheng, Bah Hwee Gwee, "GNNReveal: A Novel Graph Neural Network-based Attack Method for IC Logic Gate De-Camouflaging" in IEEE Intelligent Systems, 2024